まずは挨拶

某って、貴方はN教官でいらっしゃいますね?というかこんなこと聞いてくるのはたぶんに貴方しかいないはず。ということで某=Nと決 め付けて以下話を進めさせていただきます。と いうわけでどうもこんにちは。年末年始にゃ挨拶にも行けずじまいです いません。相変わらずあたふたしてらっしゃるのですか?超伝導体は元気に回ってますか?噂によるとwindows機でもCPUパワーが1GHz弱あればデ ジタルPIDの10msecは余裕で回せるらしいですよ。RTLinuxなら1msecも夢じゃないのでは?

というかですね、機械工学科出身の僕にこんなこと聞かれても困っちゃうわけで。どう考えてもバリバリの門外漢じゃないですか。どうせなら熱とか流体とか機械設計の話にしてください。その時は貴方の意向などお構いなしに勢い任せに語りつくしますから。

というか、高校すら卒業したことも無い馬鹿にそんなこと聞かれても、その、なんだ、困る。

しかし、聞かれたことには何でも応えないと気がすまないので一応分かる範囲で無責任にお答えします。

TDPとは

で、まずはTDPで すか。本当はめっさクレバーなのにあえて馬鹿を装うことで生徒を手玉に取るのを生業としているN先生らしい質問ですね。本当は何が何だか分かりきっている のでしょう(・∀・)ニヤニヤえーっとですね、TDPっつうとThermal Design Powerの略だったと思うのですが直訳するに熱設計電力ですね。

「最悪この程度の発熱がありますので覚悟してください」

「この石をTDPで発熱するヒーターだと見立ててください」

の意です。

それはもうCPU負荷なんぞ100%で、かつパイプラインもすっ止まることなくコアがブンブン回っているときの消費電力&発熱量を意味します。

ですから例えばマザボのベンダーならボルテージレギュレータの容量や基板周りの熱設計をTDPを参考にするでしょうし、筐体やCPUクーラーの熱設計もそれに準ずるでしょう。

では次の課題「なんで,クロックが上がって消費電力があがるか分からん.」

についてですが、それだけじゃ面白くないんでもう少し風呂敷を広げて「なぜCPUの消費電力は増えるのか?」について小生が分かる範囲でご説明致します。

この問題に対するアプローチは以下に示すとおり二通りございます。

- 高クロック化するために増大する消費電力

- 高クロック化したがために増大する消費電力

高クロック化手法と消費電力

まず、一つ目の高クロック化するために増大する消費電力についてですが、高クロック化するために回路規模を大きく取らざるをえない場合があります。「回路規模が大きくなるとクリティカルパスは伸びるわ遅延時間が積算されるわで逆に高クロックが阻まれるのでは?それに熱的な外乱も大きくなっちゃうぞ」

と いう意見もございましょうが、例えば最近のトレンドに沿ってRISCプロセッサのロジック回路のパイプライン段数(深度)を深々ととったらどうなるでしょ う?パイプライン処理とは流れ作業のことですが、作業を分割することでクリティカルパスは短縮され、容易に?高クロック化を達成できます。ですが回路の設 計は困難を極め、回路規模が大きくなること請け合いです。

ちなみにその最大手といっていいのがインテルお得意のネットバーストアーキテク チャーの究極形態であるプレス子たんです。6GHz程度を視野に入れて設定され失敗したというあの怒涛のもっさり31段スーパーパイプラインにかかれば PCも立派な暖房器具に早変わり!寒冷地帯に住む人々に安らぎの暖かさとコンピュー ティングパワーをお届けします。

(注1:プレス子たんの温もりの半分はお漏らし成分でできています。)

(注2:もっさりとはレイテンシが大きいという意。P4は高クロックからくる広帯域でスループットを稼ぐのだ。分岐ミスや反面キャッシュミスしたときのペナルティーは大きい。)

またクロックとは直接的に関係ありませんが処理速度を上げるためにキャッシュを大量に搭載しようとすると直感的に理解できるようにこれまた載せた分だけ電気は食います。

た だ、これに関しては設計思想の問題でして、例えばキャッシュを大量に積んでヒット率を上げてパイプラインストールを低減することでIPCを高め、ダウンク ロックすれば処理速度を落とすことなく消費電力を低減することも可能でしょう。つまり、コア以外の回路はそんなに高周波ではない(エクスターナルクロック 程度)ので規模が増えてもさほど電気は食いませんよということです。

あと一つの高クロック化の手法としてプロセスルールの微細化が挙げられ ます。後に詳細に語ります(これが本題)が、ロジック回路を作るならTTLかCMOSを使うのがポピュラーですよね?特に最近は燃費の良いCMOSが巷で 大流行、ナウなヤングにも馬鹿ウケしています。で、CMOSでULSIなどつくろう物なら構造上、全身これ寄生容量だらけなのです。ともかく、この寄生容 量のせいで(消費電力×遅延時間)が一定値になるというトレードオフの関係があるんですよ。だから寄生容量を減らして消費電力と高クロック化を高次元で両 立すためにプロセスルールを微細化するんですね。もちろん、プロセスルールの微細化は歩留まりの劇的な向上にもつながります。さらには配線のインダクタン スと供にスパイク電流までもが低減されるでしょう。まさに良いこと尽くめです。

ですがまあこの手の上手い話は長く続かないもので、皮肉にも 最近は度を過ぎて微細化してしまったもんですからトンネル効果によってグランドにすり抜けていく無駄電流が指数関数的に増加して困っているんです。一昔前 のプレス子たんのお漏らし属性はここに起因します。ちなみに最近のステッピングですとけっこう良い感じらしいです。

自作PCで オーバークロックするときに当てずっぽうでCPU駆動電圧を電気的&熱的限界寸前まで上げるという手法があります。(危ないのでお奨めできませんのであし からず)これは電圧を上げた分だけHighレベルの理論信号を保障しますので信号の信頼性だけがちょっと上がりますが、他の信頼性はガタ落ちです。ちなみ に消費電力は電圧の2乗に比例すると覚えておけばこれがどれほど無謀な挑戦かが分かります。

逆に勘違いしやすいのですが電圧を落 とすことでCPUが速く動くこともできます。もちろんこれだけでは誤作動するだけです。卓越した設計技術と生産 技術の下にS/N比を高く取ることでノイズマージンを減らし、しきい電圧を狭く取り、さらに駆動電圧を下げます。こうすることで信号振幅を小さく取ること で高速応答が可能となるのです。最近メモリがDDR2になって電圧が下がりましたがたぶんこういうことだと思ってます。

次は本題の「高クロック化したがために増大する消費電力」ですが、ここまで話したら先生ならなぜクロック周波数と消費電力が比例するのか理解できたはず。

MOS-FETの消費電力

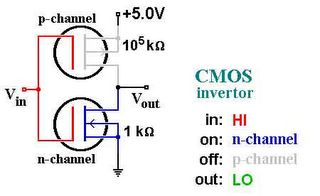

これまではなぜCMOSが電力を消費するのかについてはその理屈を避けて解説していきました。以下にCMOSの単位素子の構造を示します。P 型,N型,2対のMOS-FETでComplementaryMOSは構成されます。ゲートに印加される信号Vinの高低によりVoutの出力はHigh(この場合5V)とLow(この場合グランド)を選べます。CMOSの消費電力とは(電圧Vin)×(グランドに流れ込んだ電流Iin)で決定します。Voutよ り出て行った電流は他の素子で消費される分なのでこの素子で消費する電力には加算しません。グランドへの電流の入り口はHigh側とゲート側がありますのでまずはHigh側から解説していきましょう。

CMOSの消費電力にはスタティックな、つまりスイッチングしていないときの消費電力と、ダイナミックな過渡域での消費電力とに問題を切り分けると俄然スマートです。

ま ず、以下のように二つのトランジスタペアを流れて漏れる電流について考えましょう。

スタティックな状態、つまりゲート電圧がグランドないしVhighのときは一つのMOS-FETチャンネルは完全にONでもう一つのチャンネルはOFFになっています。この時のリーク電流がCMOSデバイスの静的なベース消費電力です。

次に過渡期での消費電力ですが、ゲートへの信号が中途半端な場合、つまりスイッチングの途中では両チャンネルが中途半端にONでもOFFでもない状態になります。このとき電流はグランドへ駄々漏れなんですが一瞬なのでさほど影響はございません。

次 はもっとダイナミックに逝きます。まずはこのFig1のMOS-FETをよーくご覧下さい。するとどうでしょう、FETがいつの間にかコンデ ンサーに見えてきたじゃありませんか!ロジックシンボルとして も似ているのですがFETはゲートという平面をメタルオキサイドという名の誘電体で絶縁したまさにコンデンサーであります。ならば、周波数に比例して、電 場の時間微分に比例して、グランドに電流駄々漏れですよね?

結局CPUの消費電力はΣ[(寄生容量)×(電圧)^2×(作動周波数)×(定数)]になるわけです。

そ れとMOS容量以外にもPN接合面やら近接した配線やら、容量性負荷なんぞいたるところにありますから隙あらばどっからでも電流は逃げます。ちなみに MOSに遅延時間が発生するのは寄生容量に電荷をチャージするのに時間がかかるからであり、オーバークロック時に電圧を上げるのは電荷のチャージを高速に 行うためであります。だから消費電力と動作速度はトレードオフになるんですよ。そして製造プロセスを微細化すれば負荷容量も小さくなるから良いんですね。 もし負荷容量が0になったら速度無限大の消費電力零のプロセッサが!?無理だろうけどね。

あ~疲れた。

参考文献;超高速CMOSロジックIC活用法

半導体デバイスアルテ21

ケンジ

間違いを発見したらジャンジャンメールで通報してください。全世界へ恥を発信したくないんで。

0 件のコメント:

コメントを投稿